Field Programmable Gate Arrays are a wonderful piece of hardware. They can act like a simple 74xx logic IC or a lowest-latency audio-mixing-device or – without changing hardware but only a new bitstream – they can be a complete microcontroller. Within the Behringer X32 two different types of FPGAs are used – depending on the production date. The earlier devices are using a Xilinx Spartan 3A while the more recent devices are using a Lattice ECP5 FPGA.

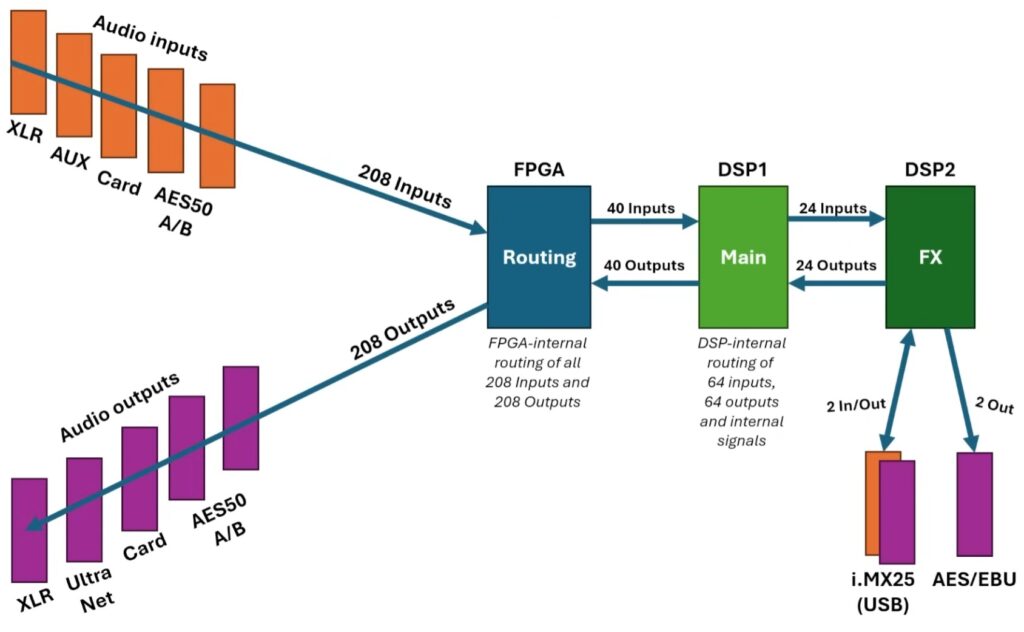

This FPGA is the heart of the digital distribution and connection within the audio-mixing-console. It collects the individual TDM-audio-connections from the ADC-boards and routes them to the digital signal processors and vice versa to the DAC-boards:

Next to the audio-signals the FPGA routes some digital communication-lines like UART and SPI as well:

But there are two more complex parts in the FPGA next to basic signal-routing. As the X32 Fullsize has an UltraNet-connector at its back, you can connect one of the P16-M personal-mixers or digital speakers. UltraNet is leaned on the AES3 or AES/EBU-protocol. AES3 is widely used in consumer-electronics with two channels between 44.1kHz and 96kHz. But the specification allows the usage of up to 192kHz and two channels.

Behringer adapted this specification and transmits 4 stereo-channels with 48kHz as a „fake“ 2-channel 192kHz transmission. You can find more information on my blog-entry here: Hacking Behringers Ultranet for a FPGA-based DIY-Audiomixer

On the right you can see the part within the FPGA that receives 2x 8 audio-channels and encodes the AES3 datastream.

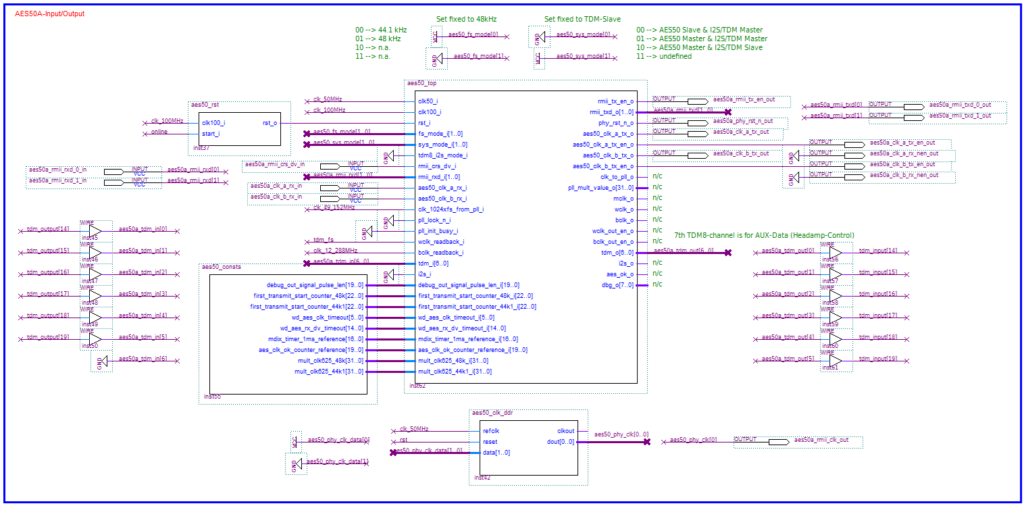

Another digital connection is the AES50 – or SuperMAC – connection. Based on common 100MBit ethernet 48 uncompressed audio-channels can be sent or received with a latency of only 3 samples.

Since end of 2025 Markus Noll has published his implementation of AES50 on GitHub as OpenSource: AES50 VHDL IP. On the left you can see the implementation within the FPGA. The IP-block takes 6 TDM-audio-streams and outputs another 6 TDM-streams. NExt to these 48 audio-channels an additional TDM-stream is used to transmit encoded auxiliary control-data used for the device-recognition and the headamp-control.

Within the AES50 specification ethernet frames are suggested, but Behringer used a plain UART-like communication on this additional AUX-channel.

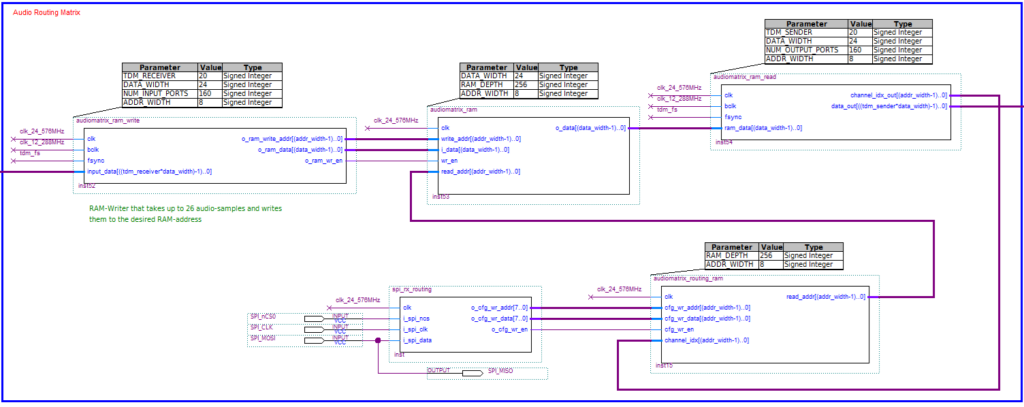

The FPGA has another – very important – function: the routing of all inputs to all possible outputs. Since version 4 of the original firmware not only blocks of 8 channels are possible, but individual channel-routings. On our open-source implementation of the firmware we are supporting this channel-by-channel routing as well. In the following picture you can see our approach: all incoming audio-channels are written to a dual-port RAM-block. After writing all 208 audio-channels, the output-block reads depending on the routing-configuration from the 208 channels and distributes them to the individual output-channels. The routing is configured by the i.MX25 main-processor via SPI-communication:

Two additional ICs are configured using the FPGA as well: the external PLL-IC and the one (or two) AUX-ADC/DAC-ICs. Why one or two? In the older series Behringer used a CirrusLogic CS42438 6-In and 8-out AD/DA-Converter-IC. In the more recent versions of the X32 they moved to a dedicated input-IC (Midas M8000) and output-IC (TI PCM1690). The next picture shows our implementation of the separated M8000/PCM1690 version using SPI-communication within the FPGA:

So, 10 months after starting reverse engineering the X32, almost all parts of the FPGA are ready. Due to the logic-demand of the AES50-core we are limited to a single AES50-port at the moment, but we are optimistic, that we are able to optimize the core in the future, so that we can enable the second AES50-port as well.